RoHS

COMPLIANT

HALOGEN

FREE

**Vishay Siliconix**

# Low-Voltage, Low R<sub>ON</sub>, Dual DPDT Analog Switch

#### DESCRIPTION

The DG2017 is a dual DPDT (double-pole/double-throw), optimized for high performance analog switching, and specifically designed to benefit portable audio applications.

One pair of double-throw switches is sub 1  $\Omega$  for low impedance speaker performance while the second pair of double-throw switches is suitable for microphone applications.

With the DPDT configuration, the DG2017 provides the flexibility for stereo-single-end or differential BTL output structures with a fully integrated differential microphone switching solution.

The DG2017 is an integrated monolithic device in a QFN-16 (4 mm x 4 mm) package that provides a space saving solution over the use of multiple single SPDT devices as well as providing the advantage of on-resistance flatness and matching that single SPDT devices cannot offer.

The DG2017 provides low charge injection (2 pC), fast switching time ( $t_{ON}$  and  $t_{OFF}$  less than 100 ns), excellent Off-Isolation and Crosstalk (- 70 dB at 100 kHz). During operation, continuous current through any or all switches is rated at ± 200 mA, ideal for portable audio applications.

Built on Vishay Siliconix's low voltage CMOS process, the DG2017 contains an epitaxial layer that prevents latchup. Break-before-make is guaranteed. When on, each switch conducts equally well in both directions, and block up to the power supply level when off.

#### FEATURES

- Halogen-free according to IEC 61249-2-21

Definition

- Low voltage operation (2 V to 5.5 V)

- Low on-resistance at 2.7 V R<sub>ON</sub>: SW<sub>1</sub>, SW<sub>2</sub> - 3.2 Ω SW<sub>3</sub>, SW<sub>4</sub> - 0.64 Ω

- Fast switching:  $t_{ON} = 46 \text{ ns}$  $t_{OFF} = 21 \text{ ns}$

- QFN-16 (4 mm x 4 mm) package

- Compliant to RoHS Directive 2002/95/EC

#### BENEFITS

- · Space saving solution

- Low power consumption

- Guaranteed low voltage operation

- Low voltage logic compatible

#### APPLICATIONS

- Cellular Phones

- Integrated Speaker Switching

- · Audio and Video Signal Routing

- PCMCIA Cards

- · Battery Operated Systems

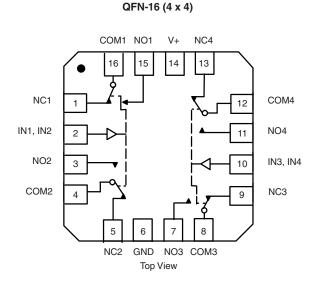

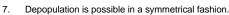

### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

| TRUTH TABLE |                 |                 |  |  |  |  |

|-------------|-----------------|-----------------|--|--|--|--|

| Logic       | NC1, 2, 3 and 4 | NO1, 2, 3 and 4 |  |  |  |  |

| 0           | ON              | OFF             |  |  |  |  |

| 1           | OFF             | ON              |  |  |  |  |

| ORDERING INFORMATION |                       |                |  |  |  |

|----------------------|-----------------------|----------------|--|--|--|

| Temp Range           | Package               | Part Number    |  |  |  |

| - 40 °C to 85 °C     | 16-pin QFN (4 x 4 mm) | DG2017DN-T1-E4 |  |  |  |

Document Number: 72228 S11-1185-Rev. B, 13-Jun-11 www.vishay.com

1

| <b>ABSOLUTE MAXIMUM RATINGS</b> ( $T_A = 25 \text{ °C}$ , unless otherwise noted) |                          |      |  |  |  |  |

|-----------------------------------------------------------------------------------|--------------------------|------|--|--|--|--|

| Parameter                                                                         | Limit                    | Unit |  |  |  |  |

| Reference V+ to GND                                                               | - 0.3 to + 6             |      |  |  |  |  |

| IN, COM, NC, NO <sup>a</sup>                                                      | - 0.3 to (V+ + 0.3)      | V    |  |  |  |  |

| Current (Any terminal except NO, NC or C                                          | 30                       | mA   |  |  |  |  |

| Continuous Current (NO, NC, or COM)                                               | ± 200                    |      |  |  |  |  |

| Peak Current (Pulsed at 1 ms, 10 % duty                                           | ± 300                    |      |  |  |  |  |

| Storage Temperature (D Suffix)                                                    | - 65 to 150              | •••  |  |  |  |  |

| Package Solder Reflow Conditions <sup>d</sup>                                     | 16-pin QFN (4 mm x 4 mm) | 240  |  |  |  |  |

| Power Dissipation (Packages) <sup>b</sup>                                         | 1880                     | mW   |  |  |  |  |

Notes:

a. Signals on NC, NO, or COM or IN exceeding V+ will be clamped by internal diodes. Limit forward diode current to maximum current ratings. b. All leads welded or soldered to PC Board.

c. Derate 23.5 mW/°C above 70 °C.

d. Manual soldering with iron is not recommended for leadless components. The QFN is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper lip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.

|                                       |                                                            | Test Conditions<br>Otherwise Unless Specified                                          |                    | <b>Limits</b><br>- 40 °C to 85 °C |                   |                   |      |

|---------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------|-----------------------------------|-------------------|-------------------|------|

| Parameter                             | Symbol                                                     | V+ = 3 V, $\pm$ 10 %, V <sub>IN</sub> = 0.4 V or 1.6 V <sup>e</sup>                    | Temp. <sup>a</sup> | Min. <sup>b</sup>                 | Typ. <sup>c</sup> | Max. <sup>b</sup> | Unit |

| Analog Switch                         |                                                            |                                                                                        |                    |                                   |                   |                   |      |

| Analog Signal Range <sup>d</sup>      | V <sub>NO</sub> , V <sub>NC</sub><br>V <sub>COM</sub>      |                                                                                        | Full               | 0                                 |                   | V+                | v    |

| DC Characteristics                    | •                                                          |                                                                                        |                    |                                   |                   |                   |      |

| On-Resistance                         | ${\sf R}_{\sf ON}$<br>(SW <sub>1</sub> , SW <sub>2</sub> ) | V+ = 2.7 V, V <sub>COM</sub> = 0.2 V/1.5 V, I <sub>NO</sub> , I <sub>NC</sub> = 10 mA  | Room<br>Full       |                                   | 3.2               | 3.7<br>4.3        |      |

| Oli-nesistance                        | R <sub>ON</sub><br>(SW <sub>3</sub> , SW <sub>4</sub> )    | V+ = 2.7 V, V <sub>COM</sub> = 0.2 V/1.5 V, I <sub>NO</sub> , I <sub>NC</sub> = 100 mA | Room<br>Full       |                                   | 0.67              | 1.1<br>1.2        |      |

| R <sub>ON</sub> Flatness <sup>d</sup> | R <sub>ON</sub><br>(SW <sub>1</sub> , SW <sub>2</sub> )    | V+ = 2.7 V, V <sub>COM</sub> = 0.2 V/1.5 V, I <sub>NO</sub> , I <sub>NC</sub> = 10 mA  | Room<br>Full       |                                   | 1.4               | 2                 |      |

|                                       | R <sub>ON</sub><br>(SW <sub>3</sub> , SW <sub>4</sub> )    | V+ = 2.7 V, V <sub>COM</sub> = 0.2 V/1.5 V, I <sub>NO</sub> , I <sub>NC</sub> = 100 mA | Room<br>Full       |                                   | 0.12              | 0.3               | Ω    |

| d                                     | $\Delta R_{ON}$<br>(SW <sub>1</sub> , SW <sub>2</sub> )    | V+ = 2.7 V, V <sub>COM</sub> = 0.2 V/1.5 V, I <sub>NO</sub> , I <sub>NC</sub> = 10 mA  | Room<br>Full       |                                   |                   | 0.3               |      |

| R <sub>ON</sub> Match <sup>d</sup>    | $\Delta R_{ON}$<br>(SW <sub>3</sub> , SW <sub>4</sub> )    | V+ = 2.7 V, V <sub>COM</sub> = 0.2 V/1.5 V, I <sub>NO</sub> , I <sub>NC</sub> = 100 mA | Room<br>Full       |                                   |                   | 0.3               |      |

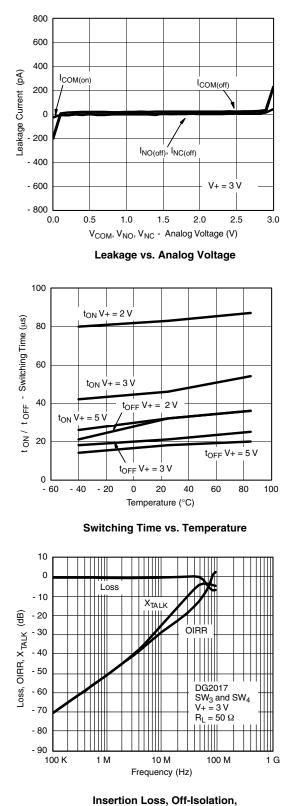

| Switch Off                            | I <sub>NO(off)</sub><br>I <sub>NC(off)</sub>               | V+ = 3.3 V                                                                             | Room<br>Full       | - 0.5<br>5                        |                   | 0.5<br>5          |      |

| Leakage Current                       | I <sub>COM(off)</sub>                                      | $V_{NO}$ , $V_{NC} = 0.3 \text{ V/3 V}$ , $V_{COM} = 0.3 \text{ V/3 V}$                | Room<br>Full       | - 0.5<br>5                        |                   | 0.5<br>5          | nA   |

| Channel-On<br>Leakage Current         | I <sub>COM(on)</sub>                                       | V+ = 3.3 V, V <sub>NO</sub> = V <sub>NC</sub> , V <sub>COM</sub> = 0.3 V/3 V           | Room<br>Full       | - 0.5<br>5                        |                   | 0.5<br>5          |      |

| Digital Control                       |                                                            |                                                                                        |                    |                                   |                   |                   |      |

| Input High Voltage                    | V <sub>INH</sub>                                           |                                                                                        | Full               | 1.6                               |                   |                   | v    |

| Input Low Voltage                     | V <sub>INL</sub>                                           |                                                                                        | Full               |                                   |                   | 0.4               | v    |

| Input Capacitance                     | C <sub>in</sub>                                            |                                                                                        | Full               |                                   | 6                 |                   | pF   |

| Input Current                         | I <sub>INL</sub> or I <sub>INH</sub>                       | V <sub>IN</sub> = 0 V or V+                                                            | Full               | - 1                               |                   | 1                 | μA   |

www.vishay.com 2

Document Number: 72228 S11-1185-Rev. B, 13-Jun-11

|                                                              |                                                           | Test Conditions<br>Otherwise Unless Specified                       |                    | <b>Limits</b><br>- 40 °C to 85 °C |                   |                   |      |

|--------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------|--------------------|-----------------------------------|-------------------|-------------------|------|

| Parameter                                                    | Symbol                                                    | V+ = 3 V, $\pm$ 10 %, V <sub>IN</sub> = 0.4 V or 1.6 V <sup>e</sup> | Temp. <sup>a</sup> | Min. <sup>b</sup>                 | Typ. <sup>c</sup> | Max. <sup>b</sup> | Uni  |

| Dynamic Characteristics                                      | · · ·                                                     |                                                                     |                    |                                   |                   |                   |      |

| Turn-On Time                                                 | $^{t_{ON}}_{(SW_1, SW_2)}$                                |                                                                     | Room<br>Full       |                                   | 62                | 85<br>91          | - ns |

| ium-On time                                                  | $^{t_{ON}}_{(SW_3, SW_4)}$                                |                                                                     | Room<br>Full       |                                   | 46                | 74<br>79          |      |

| T                                                            | $t_{ON}$<br>(SW <sub>1</sub> , SW <sub>2</sub> )          | $V_{NO}$ or $V_{NC}$ = 2 V, $R_L$ = 300 $\Omega$ , $C_L$ = 35 pF    | Room<br>Full       |                                   | 12                | 35<br>36          |      |

| Turn-Off Time                                                | t <sub>ON</sub><br>(SW <sub>3</sub> , SW <sub>4</sub> )   | (fig. 1, 2)                                                         | Room<br>Full       |                                   | 21                | 46<br>48          |      |

| Durch Defers Males Time                                      | t <sub>d</sub><br>(SW <sub>1</sub> , SW <sub>2</sub> )    |                                                                     | Full               | 5                                 | 45                |                   |      |

| Break-Before-Make Time                                       | t <sub>d</sub><br>(SW <sub>3</sub> , SW <sub>4</sub> )    |                                                                     | Full               | 5                                 | 26                |                   |      |

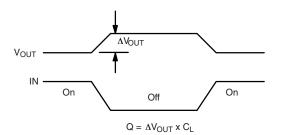

| Charge Injection <sup>d</sup>                                | $\begin{array}{c} Q_{INJ} \ (SW_1,SW_2) \end{array}$      | $C_L$ = 1 nF, $V_{GEN}$ = 0 V, $R_{GEN}$ = 0 $\Omega$               | Room               |                                   | 2                 |                   | рС   |

|                                                              | $\begin{array}{c} Q_{INJ} \ (SW_3,SW_4) \end{array}$      | (fig. 3)                                                            |                    |                                   | 1                 |                   |      |

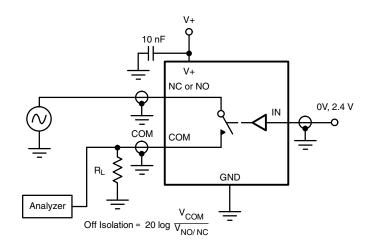

| Off-Isolation <sup>d</sup>                                   | OIRR<br>(SW <sub>1</sub> , SW <sub>2</sub> )              | R <sub>L</sub> = 50 Ω, C <sub>L</sub> = 5 pF, f = 1 MHz<br>(fig. 4) | Room               |                                   | - 68              |                   | dB   |

|                                                              | OIRR<br>(SW <sub>3</sub> , SW <sub>4</sub> )              |                                                                     |                    |                                   | - 51              |                   |      |

| Crosstalk <sup>d</sup>                                       | X <sub>TALK</sub><br>(SW <sub>1</sub> , SW <sub>2</sub> ) |                                                                     |                    |                                   | - 69              |                   |      |

| CIUSSIAIK                                                    | X <sub>TALK</sub><br>(SW <sub>3</sub> , SW <sub>4</sub> ) |                                                                     |                    |                                   | - 51              |                   |      |

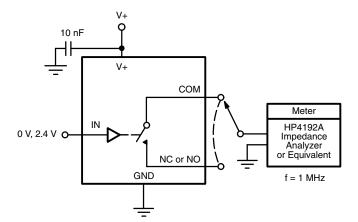

| N <sub>O</sub> , N <sub>C</sub> Off Capacitance <sup>d</sup> | $C_{OFF}$ (SW <sub>1</sub> , SW <sub>2</sub> )            | V <sub>IN</sub> = 0 V or V+, f = 1 MHz                              | Room               |                                   | 12                |                   | - pF |

| N <sub>O</sub> , N <sub>C</sub> Off Capacitance <sup>2</sup> | $\begin{array}{c} C_{OFF} \ (SW_3,SW_4) \end{array}$      |                                                                     |                    |                                   | 43                |                   |      |

| Channel-On Capacitance <sup>d</sup>                          | $\begin{array}{c} C_{ON} \ (SW_1, SW_2) \end{array}$      |                                                                     |                    |                                   | 86                |                   |      |

|                                                              | $\begin{array}{c} C_{ON} \ (SW_3,SW_4) \end{array}$       |                                                                     |                    |                                   | 283               |                   |      |

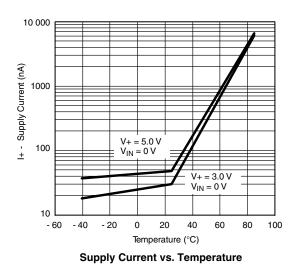

| Power Supply                                                 |                                                           |                                                                     |                    |                                   |                   |                   |      |

| Power Supply Range                                           | V+                                                        |                                                                     |                    | 2                                 |                   | 5.5               | V    |

| Power Supply Current                                         | l+                                                        | $V_{OE} = 0 V \text{ or } V+$                                       |                    |                                   |                   | 1                 | μA   |

Notes:

a. Room = 25  $^\circ\text{C},$  full = as determined by the operating suffix.

b. Typical values are for design aid only, not guaranteed nor subject to production testing.

c. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

d. Guarantee by design, nor subjected to production test.

e. VIN = input voltage to perform proper function.

f. Guaranteed by 5 V leakage testing, not production tested.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

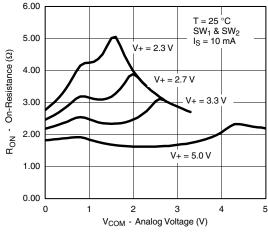

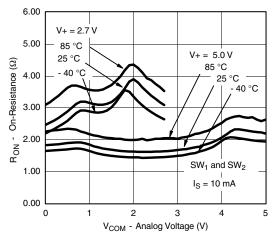

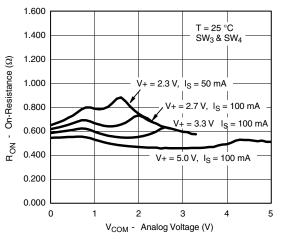

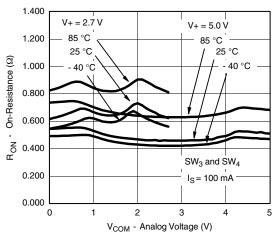

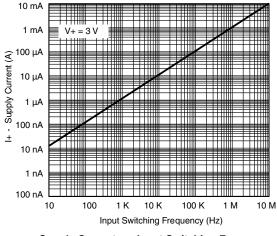

### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

$\rm R_{ON}$  vs.  $\rm V_{COM}$  and Single Supply Voltage

R<sub>ON</sub> vs. Analog Voltage and Temperature

$\mathbf{R}_{\text{ON}}$  vs.  $\mathbf{V}_{\text{COM}}$  and Single Supply Voltage

R<sub>ON</sub> vs. Analog Voltage and Temperature

Supply Current vs. Input Switching Frequency

www.vishay.com 4 Document Number: 72228 S11-1185-Rev. B, 13-Jun-11

# DG2017 Vishay Siliconix

## TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

Crosstalk vs. Frequency

Document Number: 72228 S11-1185-Rev. B, 13-Jun-11

www.vishay.com 5

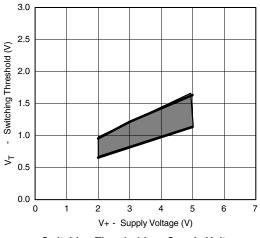

## TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

Switching Threshold vs. Supply Voltage

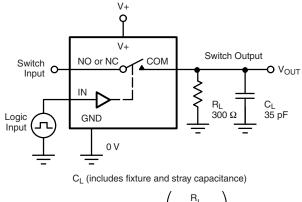

### **TEST CIRCUITS**

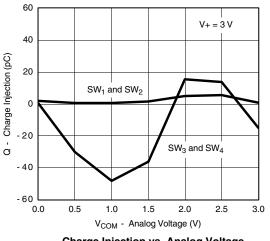

Charge Injection vs. Analog Voltage

Logic "1" = Switch On Logic input waveforms inverted for switches that have the opposite logic sense.

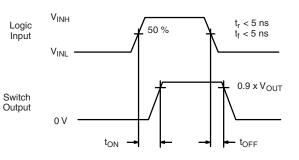

#### Figure 1. Switching Time

C<sub>L</sub> (includes fixture and stray capacitance)

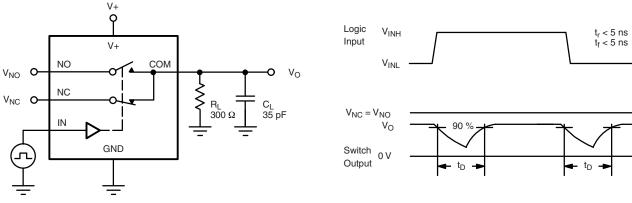

#### Figure 2. Break-Before-Make Interval

www.vishay.com 6 Document Number: 72228 S11-1185-Rev. B, 13-Jun-11

DG2017 Vishay Siliconix

### **TEST CIRCUITS**

IN depends on switch configuration: input polarity determined by sense of switch.

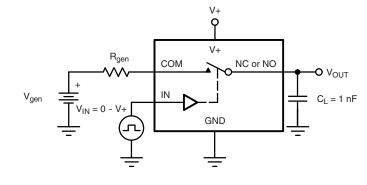

Figure 3. Charge Injection

Figure 4. Off-Isolation

Figure 5. Channel Off/On Capacitance

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?72228">www.vishay.com/ppg?72228</a>.

Document Number: 72228 S11-1185-Rev. B, 13-Jun-11 This document is subject to change without potice

Package Information Vishay Siliconix

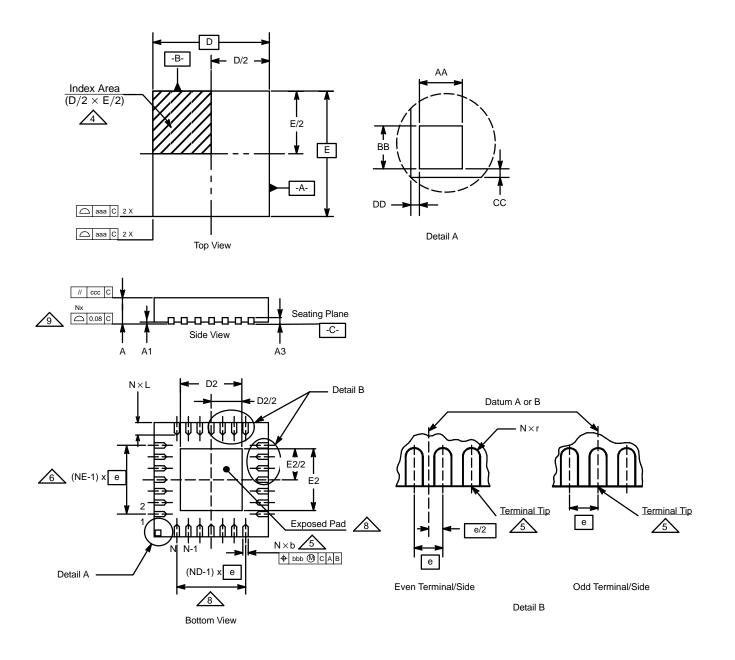

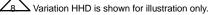

### QFN-16 (4×4 mm) JEDEC Part Number: MO-220

#### QFN-16 (4×4 mm)

JEDEC Part Number: MO-220

|     | MILLIMETERS* INCHES |          | MI   | MILLIMETERS* |            |        |       |

|-----|---------------------|----------|------|--------------|------------|--------|-------|

| Dim | Min                 | Nom      | Max  | Min          | Nom        | Max    | Notes |

| А   | 0.80                | 0.90     | 1.00 | 0.0315       | 0.0354     | 0.0394 |       |

| A1  | 0                   | 0.02     | 0.05 | 0            | 0.0008     | 0.0020 |       |

| A3  | -                   | 0.20 Ref | -    | -            | 0.0079     | -      |       |

| AA  | -                   | 0.345    | -    | -            | 0.0136     | -      |       |

| aaa | -                   | 0.25     | -    | -            | 0.0098     | -      |       |

| BB  | -                   | 0.345    | -    | -            | 0.0136     | -      |       |

| b   | 0.23                | 0.30     | 0.38 | 0.0091       | 0.0118     | 0.0150 | 5     |

| bbb | -                   | 0.10     | -    | -            | 0.0039     | -      |       |

| CC  | -                   | 0.18     | -    | -            | 0.0071     | -      |       |

| CCC | -                   | 0.10     | -    | -            | 0.0039     | -      |       |

| D   |                     | 4.00 BSC |      |              | 0.1575 BSC |        |       |

| D2  | 2.00                | 2.15     | 2.25 | 0.0787       | 0.0846     | 0.0886 |       |

| DD  | -                   | 0.18     | -    | -            | 0.0071     | -      |       |

| Е   | 4.00 BSC            |          |      | 0.1575 BSC   |            |        |       |

| E2  | 2.00                | 2.15     | 2.25 | 0.0787       | 0.0846     | 0.0886 |       |

| е   |                     | 0.65 BSC |      |              | 0.0256 BSC |        |       |

| L   | 0.45                | 0.55     | 0.65 | 0.0177       | 0.0217     | 0.0256 |       |

| Ν   | 16                  |          |      | 16           |            | 3, 7   |       |

| ND  | -                   | 4        | -    | -            | 4          | -      | 6     |

| NE  | -                   | 4        | -    | -            | 4          | -      | 6     |

| r   | b(min)/2            | -        | -    | b(min)/2     | -          | -      |       |

\* Use millimeters as the primary measurement.

ECN: S-21437—Rev. A, 19-Aug-02 DWG: 5890

NOTES:

1. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

2. All dimensions are in millimeters. All angels are in degrees.

3. N is the total number of terminals.

4. The terminal #1 identifier and terminal numbering convention shall conform to JESD 95-1 SPP-012. Details of terminal #1 identifier are optional, but must be located within the zone indicated. The terminal #1 identifier may be either a molded or marked feature. The X and Y dimension will vary according to lead counts.

$\sqrt{5.2}$  Dimension b applies to metallized terminal and is measured between 0.25 mm and 0.30 mm from the terminal tip.

$\underline{/6.}$  ND and NE refer to the number of terminals on the D and E side respectively.

$\sqrt{9.}$  Coplanarity applies to the exposed heat sink slug as well as the terminals.

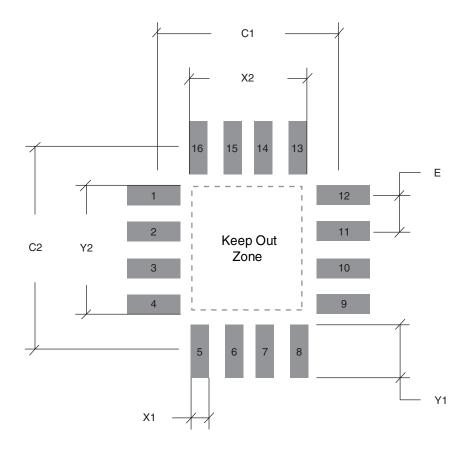

## RECOMMENDED MINIMUM PADS FOR QFN-16 (4 x 4 MM BODY)

|    | Inches | Millimeters |

|----|--------|-------------|

| C1 | 0.142  | 3.60        |

| C2 | 0.142  | 3.60        |

| E  | 0.026  | 0.65        |

| X1 | 0.014  | 0.35        |

| X2 | 0.089  | 2.25        |

| Y1 | 0.037  | 0.95        |

| Y2 | 0.089  | 2.25        |

#### Note:

QFN-16 (4 x 4) has an exposed center pad that must not come into contact with any metalized structure on the PCB. This area is considered a Keep Out Zone.

Vishay

# Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.